Проверка эквивалентности для FPGA

Систематические ошибки проектирования, вносимые инструментами автоматизированного проектирования, такими как синтез, бывает трудно обнаружить, не говоря уже о том, что они могут быть катастрофическими, если они попадут в конечное устройство. Формальная...

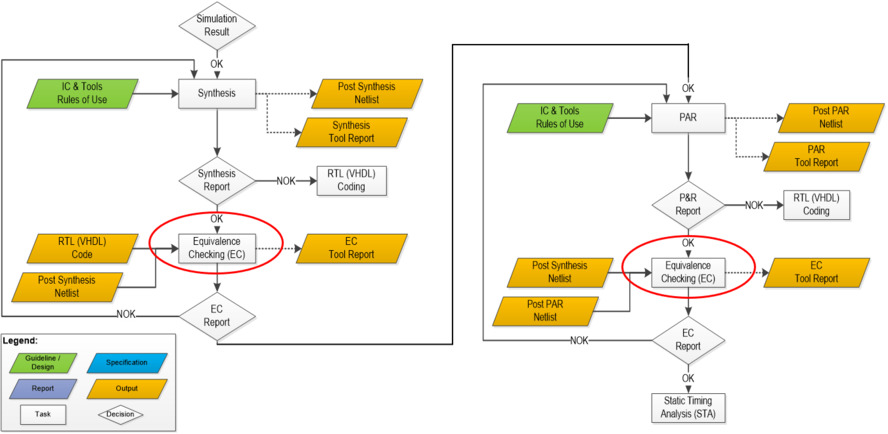

Систематические ошибки проектирования, вносимые инструментами автоматизированного проектирования, такими как синтез, бывает трудно обнаружить, не говоря уже о том, что они могут быть катастрофическими, если они попадут в конечное устройство. Формальная проверка эквивалентности использовалась при проектировании ASIC в течение многих лет. По мере увеличения логической ёмкости ПЛИС, проверка функциональной эквивалентности кода уровня RTL и окончательного проекта ПЛИС после размещения и трассировки становится критически важным и обязательным. Верификация результатов имплементации FPGA может ускорить процесс проектирования, сократить время тестирования и значительно снизить риски производства ASIC.

На вебинаре вы узнаете:

- о различиях между формальной верификацией и моделированием в контексте проверки эквивалентности

- как определить проблемы проверки для последовательной оптимизации

- обсудите преимущества подхода к верификации нетлистов и связанных с ними приложений

Вебинар состоится 27 июля 2021

Время 08:00 AM Pacific Daylight Time